处理器核心分析

外围系统架构的变革,归根到底还是为处理器内核服务。如果这一部分不作出改进,性能上的提升,也只能是一纸空文。

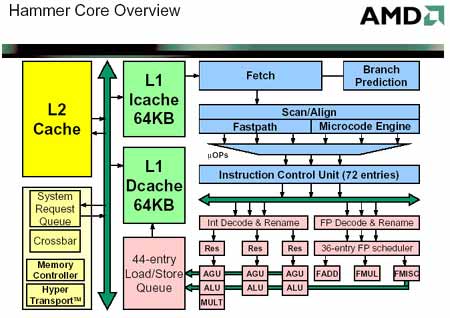

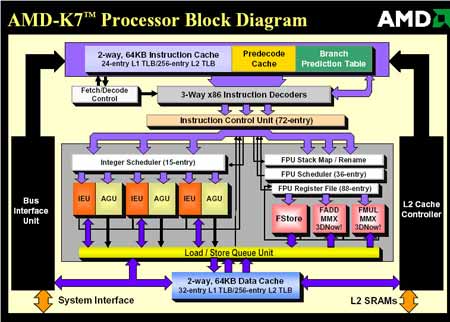

首先,我们来看两张K8核心的Athlon64(FX)与K7核心处理器的内部架构对比图:

Athlon64(FX)与K7内部架构对比

图中可见,表面上看新的核心和K7相比总体上变化并不大,同样的3个负责整数运算的ALU、AGU单元,同样的3个负责浮点、3DNow!等多媒体指令运算的浮点单元。如果不考虑新的64位指令执行状况,基本上两者处理数据的流程将非常相似。

但是较为仔细地了解了新核心的内部结构后,你会发现即使对于32位指令的执行来说,虽然他和K7相比外貌相似,实际上还是存在几处较为明显的区别的。

我们首先从前端的缓存部分入手吧:

●缓存部分的改进

一级缓存、二级缓存部分,Athlon64(FX)同K7核心相比,除了将二级缓存容量统一提升到1MB,二级缓存位宽相比K7核心的64bit倍增为128+12bit之外,并没有在结构上作出太大的变动。

然而,CPU中另一类重要缓存---主管内存地址翻译的TLB的相关参数,却在Athlon64(FX)中相对K7处理器做出了较大的变动。

为了使大家更透彻地理解TLB的参数变化对CPU性能的影响,关于TLB的原理,我们作出如下的简要介绍:

TLB的英文全名为:Translation Lookaside Buffer,我们可以翻译为旁路转换缓冲,也可以把它理解成页表缓冲,因为它里面其实存放的是一些页表文件(虚拟地址到物理地址的转换表)。

首先我们需要知道的是:TLB和我们熟悉的一级、二级缓存并没有本质的区别,二者都属于缓存一类,他们的区别在于所缓存的内容不同。我们知道,同CPU在内存中存取数据时先查找一级、二级缓存中是否存在所需的数据相同;当处理器要在内存中寻址数据时,它也不是直接到内存的物理地址里查找的,而是通过一组虚拟地址转换到主内存的物理地址。

这样,就需要有一组将虚拟地址和物理地址对应起来的地址对应表格。通常,这个表格存放在内存中,TLB则负责缓存这个表格中的数据。而CPU需要寻址数据时,同样会优先在TLB中查找是否有需要的表格数据。这样,同一级、二级缓存尺寸和联合路数对处理器性能的影响相同,处理器的性能和寻址的命中率,进而同TLB的尺寸、联合路数有很大的关系了。

对于寻址空间更大的K8,增加TLB条目数,改变TLB联合方式显然具有更重要的意义。

回到正题,我们整理了AthlonXP与Athlon64(FX)相关的TLB参数的不同之处,列出以下的表格,供大家参考:

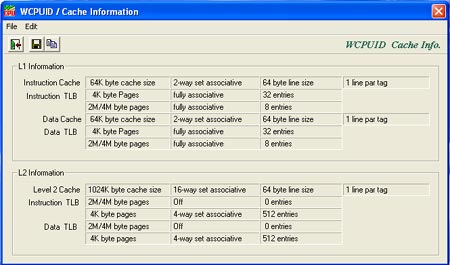

以下则是我们使用Wcpuid3.1a所测出的Athlon 64 FX51以及Athlon 64 3200+的缓存相关信息(两者信息相同,不重复贴出):

Athlon64 FX51缓存相关信息

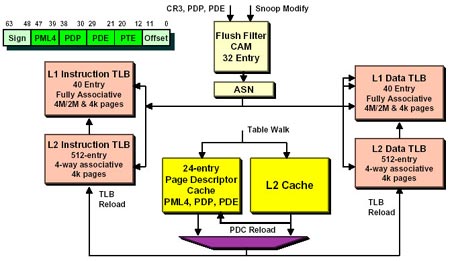

同时,在TLB控制机构方面,为了提高在程序间切换时的处理器性能,Athlon64(FX)也相应K7核心作出了一些变化。具体变化大家可以参考如下的Athlon64(FX)TLB机构图:

新的TLB控制机构