512Bit的Ring Bus记忆体控制器

除了加强了Pixel Shader引擎的效率而达至效能上升外,ATi还在新一代R520核心中改用全新的记忆体控制器技术,称为"Ring Bus Memory Controller"技术。传统显示卡技术,为了提高记忆体的传取效率,通常都会用直接提高记忆体的频宽,不过提高频宽只能为提高尖峰传送时带来便利,但如果程序并不需要太高的频宽,则更高的频宽也是枉然,情况如同只有辆车在五线限速的公路上行走,相反有效地运用记忆体宽带才是最重要。

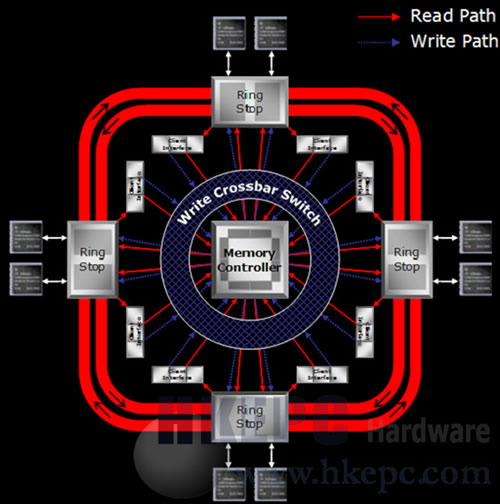

ATi R520虽然对外的频宽仍然保持合共256Bit的记忆体频宽,但内部却有一个宽阔的512Bit架构,它其实是由两个256Bit的环型管道、四个环站所组成及8组32Bit的Memory Client,每一个环站都会负责2颗32Bit的记忆体颗粒,资料会通过每一个环站直至到达所需要目的地,而两个环的走向是相对的,因此大部份情况下都只会穿过一个环站就能到达目的地,这个设计远比传统采用的Crossbar Switch更高效率,以往的CrossBar Switch在记忆体读取时,Client Interface会向记忆体控制器作出读取要求,然后控制器会作出安排并对记忆体要求读回资料到控制器,然后由控制器再传回然Cleint Interface。

但在Ring Bus的架构下,Client Interface会向记忆体控制器作出读取要求,而控制器同样会安排资料由记忆体颗粒中读取,但却不会回传至记忆体控制器,而只是把东西放在Ring Bus,然后Client Interface自行由Ring Bus取回所需要的资料封包,因此记忆体减回传的工作,减少延迟而令效率提高。

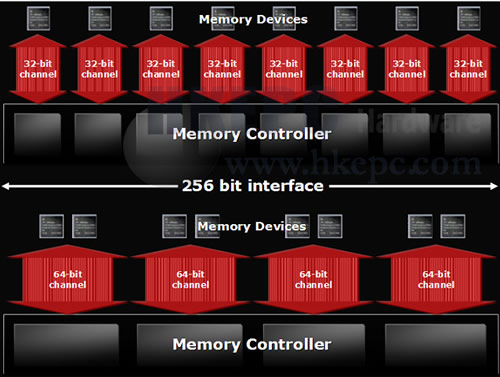

8个32Bit的记忆体通道

除了内部的Ring Bus架构,ATi亦改良了对外的记忆体频宽,图上的上方为R520的256Bit记忆体架构,而图下的是上代ATi Radeon X850架构,虽然两者都是256Bit,但X850是由4组64Bit通道组成,而R520是由8组32Bit。如果当有8个32Bit的资料要传至R520,理论上它只需要一笔的时间就能完成,但X850的64Bit并不能同时让两个32Bit资料同时传送,因此理论上需要R520一倍的时间才能完成。因此R520把通道变成8个32Bit,会令一些较零碎和细小的资料存取更效率。